# R&S®RTO Digital Oscilloscope Specifications

Data Sheet | 18.00

# **CONTENTS**

| Definitions               | 4  |

|---------------------------|----|

| Base unit                 | 5  |

| Vertical system           | 5  |

| Horizontal system         | 6  |

| Acquisition system        | 7  |

| Trigger system            | 9  |

| Waveform measurements     | 11 |

| Mask testing              | 12 |

| Waveform math             | 13 |

| Search and mark function  | 13 |

| Display characteristics   | 14 |

| Input and output          | 14 |

| General data              | 15 |

| Options                   | 16 |

| R&S®RTO-B1                | 16 |

| Vertical system           | 16 |

| Horizontal system         | 16 |

| Acquisition system        | 16 |

| Trigger system            | 16 |

| Waveform measurements     | 17 |

| Waveform math             | 17 |

| Search and mark functions | 17 |

| Display characteristics   | 17 |

| R&S®RTO-B4                | 18 |

| R&S®RTO-B10               | 18 |

| R&S®RTO-B18               | 18 |

| R&S®RTO-B19               | 18 |

| R&S®RTO-K1                | 19 |

| R&S®RTO-K2                | 20 |

| R&S®RTO-K3                | 21 |

| R&S®RTO-K4                | 22 |

| R&S®RTO-K5                | 23 |

| R&S®RTO-K6                | 24 |

| R&S®RTO-K7                | 25 |

| R&S®RTO-K9                | 26 |

| R&S®RTO-K11               | 27 |

| R&S®RTO-K12               | 28 |

| R&S®RTO-K13               | 29 |

| R&S®RTO-K17               | 30 |

2

| F  | R&S®RTO-K21        | 31   |

|----|--------------------|------|

| F  | R&S®RTO-K22        | 32   |

| F  | R&S®RTO-K23        | 33   |

|    | R&S®RTO-K24        |      |

|    | R&S®RTO-K26        |      |

| F  | R&S®RTO-K31        | 37   |

| F  | R&S®RTO-K40        | 38   |

| F  | R&S®RTO-K55        | 39   |

| F  | R&S®RTO-K60        | 40   |

| Or | dering information | . 41 |

|    |                    |      |

#### **Definitions**

#### General

Product data applies under the following conditions:

- · Three hours storage at ambient temperature followed by 30 minutes warm-up operation

- Specified environmental conditions met

- · Recommended calibration interval adhered to

- All internal automatic adjustments performed, if applicable

#### Specifications with limits

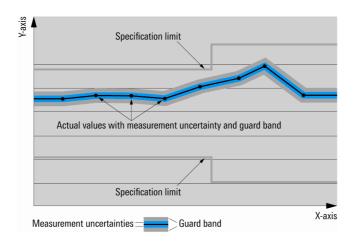

Represent warranted product performance by means of a range of values for the specified parameter. These specifications are marked with limiting symbols such as <,  $\leq$ , >,  $\geq$ ,  $\pm$ , or descriptions such as maximum, limit of, minimum. Compliance is ensured by testing or is derived from the design. Test limits are narrowed by guard bands to take into account measurement uncertainties, drift and aging, if applicable.

#### Specifications without limits

Represent warranted product performance for the specified parameter. These specifications are not specially marked and represent values with no or negligible deviations from the given value (e.g. dimensions or resolution of a setting parameter). Compliance is ensured by design.

#### Typical data (typ.)

Characterizes product performance by means of representative information for the given parameter. When marked with <, > or as a range, it represents the performance met by approximately 80 % of the instruments at production time. Otherwise, it represents the mean value.

#### Nominal values (nom.)

Characterize product performance by means of a representative value for the given parameter (e.g. nominal impedance). In contrast to typical data, a statistical evaluation does not take place and the parameter is not tested during production.

#### Measured values (meas.)

Characterize expected product performance by means of measurement results gained from individual samples.

#### **Uncertainties**

Represent limits of measurement uncertainty for a given measurand. Uncertainty is defined with a coverage factor of 2 and has been calculated in line with the rules of the Guide to the Expression of Uncertainty in Measurement (GUM), taking into account environmental conditions, aging, wear and tear.

Device settings and GUI parameters are indicated as follows: "parameter: value".

Typical data as well as nominal and measured values are not warranted by Rohde & Schwarz.

# Base unit

# **Vertical system**

| vortiour cycloni                      |                                                  |                                                                                       |

|---------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------|

| Input channels                        | R&S®RTO1002                                      | 2 channels                                                                            |

|                                       | R&S®RTO1004                                      | 4 channels                                                                            |

|                                       | R&S®RTO1012                                      | 2 channels                                                                            |

|                                       | R&S®RTO1014                                      | 4 channels                                                                            |

|                                       | R&S®RTO1022                                      | 2 channels                                                                            |

|                                       | R&S®RTO1024                                      | 4 channels                                                                            |

|                                       | R&S®RTO1044                                      | 4 channels                                                                            |

| Input impedance                       |                                                  | 50 Ω ± 2 %                                                                            |

| p p                                   |                                                  | $(50 \Omega \pm 1.5 \% \text{ from } +15 ^{\circ}\text{C to } +30 ^{\circ}\text{C}),$ |

|                                       |                                                  | $1 M\Omega \pm 1 \%    15 pF (meas.)$                                                 |

| Analog bandwidth (–3 dB)              | at 50 Ω input impedance                          |                                                                                       |

|                                       | R&S®RTO1002 and R&S®RTO1004                      | ≥ 600 MHz                                                                             |

|                                       | R&S®RTO1012 and R&S®RTO1014                      | ≥ 1 GHz                                                                               |

|                                       | R&S®RTO1022 and R&S®RTO1024                      | ≥ 2 GHz                                                                               |

|                                       | R&S®RTO1044                                      | ≥ 4 GHz                                                                               |

|                                       | at 1 MΩ input impedance                          | ≥ 500 MHz (meas.)                                                                     |

| Analog bandwidth limits               | max. –1.5 dB, min. –4 dB                         | 200 MHz, 20 MHz                                                                       |

| Rise time/fall time                   | 10 % to 90 % at 50 Ω (calculated)                | 200 1111 12, 20 1111 12                                                               |

| Tibe unichan unic                     | R&S®RTO1002 and R&S®RTO1004                      | 583 ps                                                                                |

|                                       | R&S®RTO1012 and R&S®RTO1014                      | 350 ps                                                                                |

|                                       | R&S®RTO1022 and R&S®RTO1024                      | 175 ps                                                                                |

|                                       | R&S®RTO1044                                      | 100 ps                                                                                |

| Input VSWR                            | input frequency ≤ 2 GHz                          | 1.25 (meas.)                                                                          |

| Input vovik                           | input frequency > 2 GHz                          | 1.4 (meas.)                                                                           |

| Vertical resolution                   | input frequency > 2 GHz                          | 8 bit,                                                                                |

| vertical resolution                   |                                                  | 16 bit for high resolution decimation (with                                           |

|                                       |                                                  |                                                                                       |

|                                       |                                                  | reduction of the sampling rate),                                                      |

|                                       |                                                  | 16 bit for high definition mode (without                                              |

|                                       |                                                  | reduction of the sampling rate, requires                                              |

| Effective number of hits of digitizer | for full goals give wave signal with             | the option R&S®RTO-K17) > 7.0 bit (meas.)                                             |

| Effective number of bits of digitizer | for full-scale sine-wave signal with             | > 7.0 bit (meas.)                                                                     |

|                                       | frequency equal to or lower than –3 dB bandwidth |                                                                                       |

| DC gain accuracy                      | offset and position set to 0 V, after self-ali   | gnment                                                                                |

| ,                                     | at 50 Ω, input sensitivity > 5 mV/div            | ±1.5 %                                                                                |

|                                       | at 50 Ω, input sensitivity ≤ 5 mV/div            | ±2 %                                                                                  |

|                                       | at 1 MΩ                                          | ±2 %                                                                                  |

| Input coupling                        | at 50 Ω                                          | DC and GND                                                                            |

|                                       | at 1 MΩ                                          | DC, AC and GND                                                                        |

| Input sensitivity                     | at 50 Ω                                          | 1 mV/div to 1 V/div                                                                   |

| mpat conditivity                      | at 1 MΩ                                          | 1 mV/div to 10 V/div                                                                  |

| Maximum input voltage                 | at 50 Ω                                          | 5 V (RMS)                                                                             |

| maximum input voitage                 | at 1 MΩ                                          | 150 V (RMS), 200 V (V <sub>p</sub> ),                                                 |

|                                       | GC 1 1V132                                       | derates at 20 dB/decade to 5 V (RMS)                                                  |

|                                       |                                                  | above 250 kHz                                                                         |

| Position range                        |                                                  | ±5 div                                                                                |

| Offset range at 50 Ω                  | input sensitivity                                | ±5 div                                                                                |

| Onset range at 50 12                  | 316 mV/div to ≤ 1 V/div                          | ±10 V                                                                                 |

|                                       |                                                  |                                                                                       |

|                                       | 100 mV/div to ≤ 316 mV/div                       | ±3 V                                                                                  |

| Offset range at 1 MO                  | 1 mV/div to ≤ 100 mV/div                         | ±1 V                                                                                  |

| Offset range at 1 MΩ                  | input sensitivity                                | 1/44E V input constitute of 5 dt A                                                    |

|                                       | 3.16 V/div to ≤ 10 V/div                         | ±(115 V – input sensitivity × 5 div)                                                  |

|                                       | 1 V/div to ≤ 3.16 V/div                          | ±100 V                                                                                |

|                                       | 316 mV/div to ≤ 1 V/div                          | ±(11.5 V – input sensitivity × 5 div)                                                 |

|                                       | 100 mV/div to ≤ 316 mV/div                       | ±10 V                                                                                 |

|                                       | 31.6 mV/div to ≤ 100 mV/div                      | ±(1.15 V – input sensitivity × 5 div)                                                 |

|                                       | 1 mV/div to ≤ 31.6 mV/div                        | ±1 V                                                                                  |

| Offset accuracy                       |                                                  | ±(0.35 % ×  net offset  +                                                             |

| -                                     |                                                  | 2.5 mV + 0.1 div × input sensitivity)                                                 |

|                                       |                                                  | (net offset =                                                                         |

|                                       |                                                  |                                                                                       |

| DC measurement accuracy                  | after adequate suppression of           | ±(DC gain accurac    | y ×          |

|------------------------------------------|-----------------------------------------|----------------------|--------------|

|                                          | measurement noise using high-resolution | reading – net offset |              |

|                                          | sampling mode or waveform averaging or  | + offset accuracy)   |              |

|                                          | a combination of both                   |                      |              |

| Channel-to-channel isolation             | input frequency ≤ 2 GHz                 | > 60 dB              |              |

| (each channel at same input sensitivity) | input frequency > 2 GHz                 | > 50 dB              |              |

| RMS noise floor at 50 Ω (typ.)           | input sensitivity                       | R&S®RTO1002,         | R&S®RTO1012, |

|                                          |                                         | R&S®RTO1004          | R&S®RTO1014  |

|                                          | 1 mV/div                                | 0.08 mV              | 0.10 mV      |

|                                          | 2 mV/div                                | 0.08 mV              | 0.10 mV      |

|                                          | 5 mV/div                                | 0.11 mV              | 0.12 mV      |

|                                          | 10 mV/div                               | 0.17 mV              | 0.20 mV      |

|                                          | 20 mV/div                               | 0.28 mV              | 0.36 mV      |

|                                          | 50 mV/div                               | 0.70 mV              | 0.85 mV      |

|                                          | 100 mV/div                              | 1.30 mV              | 1.65 mV      |

|                                          | 200 mV/div                              | 2.70 mV              | 3.30 mV      |

|                                          | 500 mV/div                              | 7.00 mV              | 8.70 mV      |

|                                          | 1 V/div                                 | 13.7 mV              | 17.0 mV      |

|                                          | input sensitivity                       | R&S®RTO1022,         | R&S®RTO1044  |

|                                          |                                         | R&S®RTO1024          | (meas.)      |

|                                          | 1 mV/div                                | 0.15 mV              | 0.24 mV      |

|                                          | 2 mV/div                                | 0.15 mV              | 0.25 mV      |

|                                          | 5 mV/div                                | 0.18 mV              | 0.28 mV      |

|                                          | 10 mV/div                               | 0.28 mV              | 0.42 mV      |

|                                          | 20 mV/div                               | 0.50 mV              | 0.72 mV      |

|                                          | 50 mV/div                               | 1.22 mV              | 1.80 mV      |

|                                          | 100 mV/div                              | 2.39 mV              | 3.60 mV      |

|                                          | 200 mV/div                              | 4.80 mV              | 7.20 mV      |

|                                          | 500 mV/div                              | 12.0 mV              | 18.0 mV      |

|                                          | 1 V/div                                 | 23.9 mV              | 36.0 mV      |

# **Horizontal system**

| Timebase range          |                                            | selectable between 25 ps/div and 50 s/div,                                                           |

|-------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------|

|                         |                                            | time per div settable to any value within                                                            |

|                         |                                            | range                                                                                                |

| Channel deskew          |                                            | ±100 ns                                                                                              |

| Reference position      |                                            | 10 % to 90 % of measurement display                                                                  |

|                         |                                            | area                                                                                                 |

| Trigger offset range    | max.                                       | +(memory depth/current sampling rate)                                                                |

|                         | min.                                       | -10 000 s                                                                                            |

| Modes                   |                                            | normal, roll                                                                                         |

| Channel-to-channel skew |                                            | < 100 ps (meas.)                                                                                     |

| Timebase accuracy       | standard                                   |                                                                                                      |

|                         | after delivery/calibration, at +23 °C      | ±5 ppm                                                                                               |

|                         | during calibration interval                | ±10 ppm                                                                                              |

|                         | with R&S®RTO-B4 option                     |                                                                                                      |

|                         | after delivery/calibration, at +23 °C      | ±0.02 ppm                                                                                            |

|                         | during calibration interval                | ±0.2 ppm                                                                                             |

|                         | long-term stability                        | ±(0.1 + 0.1 × years since calibration) ppm                                                           |

|                         | (more than one year since calibration)     |                                                                                                      |

| Delta time accuracy     | corresponds to time error between two      | ±(K/realtime sampling rate +                                                                         |

|                         | edges on same acquisition and channel;     | timebase accuracy ×  reading ) (peak)                                                                |

|                         | signal amplitude greater than 5 divisions, | (meas.)                                                                                              |

|                         | measurement threshold set to 50 %,         | where                                                                                                |

|                         | vertical gain 10 mV/div or greater; rise   | K = 0.15 (R&S <sup>®</sup> RTO1002, R&S <sup>®</sup> RTO1004)                                        |

|                         | time lower than four sample periods;       | K = 0.18 (R&S <sup>®</sup> RTO1012, R&S <sup>®</sup> RTO1014)                                        |

|                         | waveform acquired in realtime mode         | K = 0.25 (R&S <sup>®</sup> RTO1022, R&S <sup>®</sup> RTO1024)<br>K = 0.43 (R&S <sup>®</sup> RTO1044) |

# **Acquisition system**

| Realtime sampling rate             | R&S®RTO1002, R&S®RTO1004,                           | max. 10 Gsample/s on each channel            |

|------------------------------------|-----------------------------------------------------|----------------------------------------------|

| , ,                                | R&S®RTO1012, R&S®RTO1014,                           |                                              |

|                                    | R&S®RTO1022, R&S®RTO1024                            |                                              |

|                                    | R&S®RTO1044                                         | max. 10 Gsample/s on 4 channels,             |

|                                    |                                                     | max. 20 Gsample/s on 2 channels              |

| Realtime waveform acquisition rate | max.                                                | > 1 000 000 waveforms/s                      |

| Memory depth                       | standard                                            | 1 000 000 1101 0101 1107 0                   |

| Welliofy depth                     | R&S®RTO1002, R&S®RTO1012,                           | 20 Msample on 2 channels,                    |

|                                    | R&S®RTO1002, N&S 101012,                            | 40 Msample on 1 channel                      |

|                                    | R&S®RTO1022<br>R&S®RTO1004, R&S®RTO1014,            | · · · · · · · · · · · · · · · · · · ·        |

|                                    |                                                     | 20 Msample on 4 channels,                    |

|                                    | R&S <sup>®</sup> RTO1024, R&S <sup>®</sup> RTO1044  | 40 Msample on 2 channels,                    |

|                                    |                                                     | 80 Msample on 1 channel                      |

|                                    | R&S®RTO-B101 option                                 |                                              |

|                                    | R&S®RTO1002, R&S®RTO1012,                           | 50 Msample on 2 channels,                    |

|                                    | R&S®RTO1022                                         | 100 Msample on 1 channel                     |

|                                    | R&S®RTO1004, R&S®RTO1014,                           | 50 Msample on 4 channels,                    |

|                                    | R&S®RTO1024, R&S®RTO1044                            | 100 Msample on 2 channels,                   |

|                                    |                                                     | 200 Msample on 1 channel                     |

|                                    | R&S®RTO-B102 option                                 |                                              |

|                                    | R&S®RTO1002, R&S®RTO1012,                           | 100 Msample on 2 channels,                   |

|                                    | R&S®RTO1022                                         | 200 Msample on 1 channel                     |

|                                    | R&S®RTO1004, R&S®RTO1014,                           | 100 Msample on 4 channels,                   |

|                                    | R&S®RTO1024, R&S®RTO1044                            | 200 Msample on 2 channels,                   |

|                                    | 1103 11101024, 1103 11101044                        | 400 Msample on 1 channel                     |

|                                    | DOC®DIO D102 ention (instruments wit                |                                              |

|                                    |                                                     | h operating system Windows 7 embedded)       |

|                                    | R&S®RTO1002, R&S®RTO1012,                           | 200 Msample on 2 channels,                   |

|                                    | R&S®RTO1022                                         | 400 Msample on 1 channel                     |

|                                    | R&S <sup>®</sup> RTO1004, R&S <sup>®</sup> RTO1014, | 200 Msample on 4 channels,                   |

|                                    | R&S®RTO1024, R&S®RTO1044                            | 400 Msample on 2 channels,                   |

|                                    |                                                     | 800 Msample on 1 channel                     |

|                                    | R&S®RTO-B104 option (instruments                    | with operating system Windows 7 embedded)    |

|                                    | R&S <sup>®</sup> RTO1002, R&S <sup>®</sup> RTO1012, | 400 Msample on 2 channels,                   |

|                                    | R&S®RTO1022                                         | 800 Msample on 1 channel                     |

|                                    | R&S®RTO1004, R&S®RTO1014,                           | 400 Msample on 4 channels,                   |

|                                    | R&S®RTO1024, R&S®RTO1044                            | 800 Msample on 2 channels (restriction:      |

|                                    | ,                                                   | 400 Msample on 2 channels when Ch1           |

|                                    |                                                     | and Ch2 or Ch3 and Ch4 are turned on),       |

|                                    |                                                     | 800 Msample on 1 channel                     |

| Decimation modes                   | sample                                              | first sample in decimation interval          |

| Decimation modes                   | peak detect                                         | largest and smallest sample in decimation    |

|                                    | peak detect                                         |                                              |

|                                    | hinh need wien                                      | interval                                     |

|                                    | high resolution                                     | average value of samples in decimation       |

|                                    |                                                     | interval                                     |

|                                    | root mean square                                    | root of squared average of samples in        |

|                                    |                                                     | decimation interval                          |

| Waveform arithmetic                | off                                                 | no arithmetic                                |

|                                    | envelope                                            | envelope of acquired waveforms               |

|                                    | average                                             | average of acquired waveforms,               |

|                                    | -                                                   | max. average depth depends on                |

|                                    |                                                     | decimation mode <sup>1</sup>                 |

|                                    | sample                                              | max. 16 777 215                              |

|                                    | high resolution                                     | max. 65 535                                  |

|                                    |                                                     | max. 255                                     |

|                                    | root mean square                                    |                                              |

|                                    | reset condition                                     | no reset (standard), reset by time, reset by |

|                                    |                                                     | number of processed waveforms                |

| Waveform streams per channel       |                                                     | up to 3 with independent selection of        |

|                                    |                                                     | decimation mode and waveform arithmetic      |

<sup>1</sup> Waveform averaging is not compatible with peak detect decimation.

#### Version 18.00, November 2014

| Sampling modes       | realtime mode     | max. sampling rate set by digitizer       |

|----------------------|-------------------|-------------------------------------------|

|                      | interpolated time | enhancement of sampling resolution by     |

|                      |                   | interpolation; max. equivalent sampling   |

|                      |                   | rate is 4 Tsample/s                       |

|                      | equivalent time   | enhancement of sampling resolution by     |

|                      |                   | repetitive acquisition; max. equivalent   |

|                      |                   | sampling rate is 4 Tsample/s              |

| Interpolation modes  |                   | linear, sin(x)/x, sample&hold             |

| Ultra segmented mode |                   | continuous recording of waveforms in      |

|                      |                   | acquisition memory without interruption   |

|                      |                   | due to visualization; blind time between  |

|                      |                   | consecutive acquisitions less than 300 ns |

# **Trigger system**

| Sources        | R&S®RTO1002, R&S®RTO1012,                | channel 1, channel 2                       |

|----------------|------------------------------------------|--------------------------------------------|

|                | R&S®RTO1022                              |                                            |

|                | R&S®RTO1004, R&S®RTO1014,                | channel 1, channel 2, channel 3, channel 4 |

|                | R&S®RTO1024, R&S®RTO1044                 |                                            |

| Sensitivity    | trigger hysteresis mode                  | auto (standard) or manual                  |

|                | range                                    | 0 V to 5 div × input sensitivity           |

| Trigger jitter | full-scale sine wave of frequency set to | < 1 ps (RMS) (meas.)                       |

| ,              | -3 dB bandwidth                          |                                            |

| Coupling mode  | standard                                 | same as selected channel                   |

|                | lowpass filter                           | cutoff frequency selectable from 100 kHz   |

|                |                                          | to 50 % of analog bandwidth                |

| Sweep mode     |                                          | auto, normal, single, n single             |

| Event rate     | max.                                     | one event for every 400 ps time interval   |

| Trigger level  | range                                    | ±5 div from center of screen               |

| Holdoff range  | time                                     | 100 ns to 10 s, fixed and random           |

|                | events                                   | 1 event to 2 000 000 000 events            |

| Main trigger modes |                                                                                         |                                                                                                               |  |  |

|--------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Edge               | triggers on specified slope (posit                                                      | tive, negative or either) and level                                                                           |  |  |

| Glitch             | triggers on glitches of positive, n specified width                                     | triggers on glitches of positive, negative or either polarity that are shorter or longer than specified width |  |  |

|                    | glitch width                                                                            | 100 ps to 1000 s                                                                                              |  |  |

|                    |                                                                                         | 50 ps to 1000 s (R&S®RTO1044 only)                                                                            |  |  |

| Width              | triggers on positive or negative prinside or outside the interval                       | oulse of specified width; width can be shorter, longer,                                                       |  |  |

|                    | pulse width                                                                             | 100 ps to 1000 s                                                                                              |  |  |

|                    | , , , , , ,                                                                             | 50 ps to 1000 s (R&S®RTO1044 only)                                                                            |  |  |

| Runt               | triggers on pulse of positive, neo                                                      | gative or either polarity that crosses one threshold but                                                      |  |  |

|                    |                                                                                         | before crossing the first one again; runt pulse width                                                         |  |  |

|                    | can be arbitrary, shorter, longer,                                                      |                                                                                                               |  |  |

|                    | runt pulse width                                                                        | 100 ps to 1000 s                                                                                              |  |  |

|                    | , and passes                                                                            | 50 ps to 1000 s (R&S®RTO1044 only)                                                                            |  |  |

| Window             |                                                                                         | xits a specified voltage range; triggers also when signal ge range for a specified period of time             |  |  |

| Timeout            |                                                                                         | low or unchanged for a specified period of time                                                               |  |  |

| rimedat            | timeout                                                                                 | 100 ps to 1000 s                                                                                              |  |  |

|                    | umodi                                                                                   | 50 ps to 1000 s (R&S®RTO1044 only)                                                                            |  |  |

| Interval           | triggers when time between two                                                          | triggers when time between two consecutive edges of same slope (positive or negative)                         |  |  |

| ilitei vai         | is shorter, longer, inside or outsi                                                     |                                                                                                               |  |  |

|                    | interval time                                                                           | 100 ps to 1000 s                                                                                              |  |  |

|                    | mervar time                                                                             | 50 ps to 1000 s (R&S®RTO1044 only)                                                                            |  |  |

| Slew rate          | triggers when the time required by a signal edge to toggle between user-defined upper   |                                                                                                               |  |  |

| Olew rate          | and lower voltage levels is shorter, longer, inside or outside the interval; edge slope |                                                                                                               |  |  |

|                    | may be positive, negative or either                                                     |                                                                                                               |  |  |

|                    | toggle time                                                                             | 100 ps to 1000 s                                                                                              |  |  |

|                    | toggie time                                                                             | 50 ps to 1000 s (R&S®RTO1044 only)                                                                            |  |  |

| Data2clock         | triggers on setup time and hold t                                                       | time violations between clock and data present on any                                                         |  |  |

| Datazolock         |                                                                                         | two input channels; monitored time interval may be specified by the user in the range                         |  |  |

|                    | · ·                                                                                     | a clock edge and must be at least 100 ps wide                                                                 |  |  |

| Pattern            |                                                                                         | tion (and, nand, or, nor) of the input channels stays true                                                    |  |  |

|                    |                                                                                         | er, inside or outside a specified range                                                                       |  |  |

| State              |                                                                                         | triggers when a logical combination (and, nand, or, nor) of the input channels stays true                     |  |  |

|                    |                                                                                         | at a slope (positive, negative or either) in one selected channel                                             |  |  |

| Serial pattern     |                                                                                         | triggers on serial data pattern up to 128 bit clocked by one input channel; pattern bits                      |  |  |

| Conai pattorn      | may be high (H), low (L) or don't care (X); clock edge slope may be positive, negative  |                                                                                                               |  |  |

|                    | or either; hardware CDR selectable as clock source (requires R&S®RTO-K13 option)        |                                                                                                               |  |  |

|                    | max. data rate                                                                          | < 2.50 Gbps                                                                                                   |  |  |

|                    |                                                                                         | < 5 Gbps (R&S®RTO1044 only)                                                                                   |  |  |

| TV/video           | triggers on baseband analog pro                                                         | triggers on baseband analog progressive and interlaced video signals including NTSC,                          |  |  |

| ,                  | PAL, PAL-M, SECAM, EDTV and HDTV broadcast standards as well as custom bi-level         |                                                                                                               |  |  |

|                    | and tri-level sync video standards                                                      |                                                                                                               |  |  |

|                    | trigger modes                                                                           | all fields, odd fields, even fields, all lines,                                                               |  |  |

|                    | tilgger modes                                                                           | line number                                                                                                   |  |  |

| Advanced trigger modes           |                                                                                                                                                                                              |                                                                                                                                                       |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Trigger qualification            | trigger events may be qualified by a logical                                                                                                                                                 |                                                                                                                                                       |  |

|                                  | qualifiable events                                                                                                                                                                           | edge, glitch, width, runt, window, timeout, interval                                                                                                  |  |

| Sequence trigger (A/B/R trigger) | triggers on B event after occurrence of A event; delay condition after A event specified either as time interval or number of B events; an optional R event resets the trigger sequence to A |                                                                                                                                                       |  |

|                                  | A event                                                                                                                                                                                      | any trigger mode                                                                                                                                      |  |

|                                  | B event                                                                                                                                                                                      | edge                                                                                                                                                  |  |

|                                  | R event                                                                                                                                                                                      | edge, glitch, width, runt, window, timeout, interval, slew rate                                                                                       |  |

| Serial bus trigger               | basic                                                                                                                                                                                        | I <sup>2</sup> C, SPI, UART/RS-232                                                                                                                    |  |

|                                  | optional                                                                                                                                                                                     | LIN, CAN, FlexRay™ and I²S with dedicated software options                                                                                            |  |

| NFC trigger                      |                                                                                                                                                                                              | with R&S®RTO-K11 option                                                                                                                               |  |

| CDR trigger                      | triggers on clock signal recovered from the instant user-selectable as fraction of bit per CDR configuration parameters                                                                      | trigger source signal; phase of the trigger                                                                                                           |  |

|                                  | CDR bit rate range                                                                                                                                                                           | pg,                                                                                                                                                   |  |

|                                  | R&S®RTO1002, R&S®RTO1004,<br>R&S®RTO1012, R&S®RTO1014,<br>R&S®RTO1022, R&S®RTO1024                                                                                                           | 200 kbps to 2.5 Gbps                                                                                                                                  |  |

|                                  | R&S®RTO1044                                                                                                                                                                                  | 200 kbps to 2.5 Gpbs standard,<br>400 kbps to 5.0 Gbps when operating at<br>20 Gsample/s realtime sampling rate <sup>2</sup>                          |  |

| External trigger input           | input impedance                                                                                                                                                                              | $50 \Omega \pm 1.5 \%$ or $1 M\Omega \pm 1 \% \parallel 20 pF (meas.)$                                                                                |  |

|                                  | max. input voltage at 50 $\Omega$                                                                                                                                                            | 5 V (RMS)                                                                                                                                             |  |

|                                  | max. input voltage at 1 $M\Omega$                                                                                                                                                            | 30 V (RMS)<br>derates at 20 dB/decade to 5 V (RMS)<br>above 25 MHz                                                                                    |  |

|                                  | trigger level                                                                                                                                                                                | ±5 V                                                                                                                                                  |  |

|                                  | sensitivity                                                                                                                                                                                  | 1 == :                                                                                                                                                |  |

|                                  | input frequency ≤ 100 MHz                                                                                                                                                                    | 300 mV (V <sub>pp</sub> )                                                                                                                             |  |

|                                  | 100 MHz < input frequency ≤ 500 MHz                                                                                                                                                          | 600 mV (V <sub>pp</sub> )                                                                                                                             |  |

|                                  | input coupling                                                                                                                                                                               | AC, DC (50 Ω and 1 MΩ), GND, HF reject (attenuates > 50 kHz or > 50 MHz, user-selectable), LF reject (attenuates < 5 kHz or < 50 kHz user-selectable) |  |

|                                  | trigger modes                                                                                                                                                                                | edge (rise or fall)                                                                                                                                   |  |

| Trigger out                      | functionality                                                                                                                                                                                | a pulse is generated for every acquisition trigger event                                                                                              |  |

|                                  | output voltage                                                                                                                                                                               | 0 V to 5 V at high impedance;<br>0 V to 2.5 V at 50 Ω                                                                                                 |  |

|                                  | pulse width                                                                                                                                                                                  | selectable between 50 ns and 60 ms                                                                                                                    |  |

|                                  | pulse polarity                                                                                                                                                                               | low active or high active                                                                                                                             |  |

|                                  | output delay                                                                                                                                                                                 | depends on trigger settings                                                                                                                           |  |

|                                  | iitter                                                                                                                                                                                       | ±600 ps (meas.)                                                                                                                                       |  |

\_

<sup>&</sup>lt;sup>2</sup> The R&S®RTO1044 front-end samples at 20 Gsample/s when at most one channel from each pair {channel1, channel2} and {channel3, channel4} is active; and the user-selected sampling resolution in realtime sampling mode or interpolated time sampling mode is 50 ps or smaller.

# **Waveform measurements**

| General features     | measurement panels | up to 8 measurement panels; each panel may contain any number of automatic |

|----------------------|--------------------|----------------------------------------------------------------------------|

|                      |                    | measurements of the same category                                          |

|                      | gate               | delimits the display region evaluated for                                  |

|                      | 3                  | automatic measurements                                                     |

|                      | reference levels   | user-configurable vertical levels define                                   |

|                      | 1010101100 101010  | support structures for automatic                                           |

|                      |                    | measurements                                                               |

|                      | statistics         | displays maximum, minimum, mean,                                           |

|                      | Stationos          | standard deviation, RMS and                                                |

|                      |                    | measurement count for each automatic                                       |

|                      |                    | measurement                                                                |

|                      | track              | measurement results displayed as                                           |

|                      | llaok              | continuous trace that is time-correlated to                                |

|                      |                    | the measurement source; requires                                           |

|                      |                    | · · · · · · · · · · · · · · · · · · ·                                      |

|                      | lang term analysis | R&S®RTO-K12 option                                                         |

|                      | long-term analysis | history of selected measurements as trace                                  |

|                      | historyaya         | against count index                                                        |

|                      | histogram          | available for one measurement per                                          |

|                      | P. 11. 1           | measurement panel                                                          |

|                      | limit check        | measurements tested against user-defined                                   |

|                      |                    | margins and limits; pass or fail conditions                                |

|                      |                    | may launch automatic response:                                             |

|                      |                    | acquisition stop, beep, print and save                                     |

|                      |                    | waveform                                                                   |

| Measurement category | amplitude and time | amplitude, high, low, maximum, minimum,                                    |

|                      |                    | peak-to-peak, mean, RMS, sigma,                                            |

|                      |                    | overshoot, area, rise time, fall time,                                     |

|                      |                    | positive width, negative width, period,                                    |

|                      |                    | frequency, duty cycle, delay, phase, burst                                 |

|                      |                    | width, pulse count, positive switching,                                    |

|                      |                    | negative switching, cycle area, cycle                                      |

|                      |                    | mean, cycle RMS, cycle sigma, setup/hold                                   |

|                      |                    | time, setup/hold ratio, pulse train,                                       |

|                      |                    | DC voltmeter (requires Rohde & Schwarz                                     |

|                      |                    | active probe with R&S®ProbeMeter                                           |

|                      |                    | functionality)                                                             |

|                      | eye diagram        | extinction ratio, eye height, eye width, eye                               |

|                      |                    | top, eye base, Q factor, S/N ratio, duty                                   |

|                      |                    | cycle distortion, eye rise time, eye fall                                  |

|                      |                    | time, eye bit rate, eye amplitude, jitter                                  |

|                      |                    | (peak-to-peak, 6-sigma, RMS)                                               |

|                      | spectrum           | channel power, bandwidth, occupied                                         |

|                      |                    | bandwidth, total harmonic distortion                                       |

|                      | jitter             | cycle-to-cycle jitter, N-cycle jitter, cycle-to-                           |

|                      | Jittei             | cycle width, cycle-to-cycle duty cycle,                                    |

|                      |                    | time-interval error, data rate, unit interval,                             |

|                      |                    |                                                                            |

|                      |                    | skew delay, skew phase; requires R&S®RTO-K12 option                        |

| Cureore              | sotup              |                                                                            |

| Cursors              | setup              | up to 4 cursor sets on screen, each set                                    |

|                      |                    | consisting of two horizontal and two                                       |

|                      | An war of          | vertical cursors                                                           |

|                      | target             | acquired waveforms (input channels),                                       |

|                      |                    | math waveforms, reference waveforms,                                       |

|                      |                    | track waveforms, XY diagrams                                               |

|                      | operating mode     | vertical measurements, horizontal                                          |

|                      |                    | measurements or both;                                                      |

|                      |                    | vertical cursors either set manually or                                    |

|                      |                    | locked to waveform                                                         |

| Histogram | source                 | acquired waveform (input channels),          |

|-----------|------------------------|----------------------------------------------|

|           |                        | math waveform, reference waveform            |

|           | mode                   | vertical (for timing statistics), horizontal |

|           |                        | (for amplitude statistics)                   |

|           | automatic measurements | waveform count, waveform samples,            |

|           |                        | histogram samples, histogram peak,           |

|           |                        | peak value, maximum, minimum, median,        |

|           |                        | range, mean, sigma, mean ± 1, 2 and 3        |

|           |                        | sigma, marker ± probability                  |

# Mask testing

| Test definition                         | number of masks                | up to 8 simultaneously                                                          |  |

|-----------------------------------------|--------------------------------|---------------------------------------------------------------------------------|--|

|                                         | source                         | acquired waveforms (input channels),                                            |  |

|                                         |                                | math waveforms                                                                  |  |

|                                         | fail condition                 | sample hit or waveform hit                                                      |  |

|                                         | fail tolerance                 | minimum number of fail events for test fail                                     |  |

|                                         |                                | in range from 0 to 4 000 000 000                                                |  |

|                                         | test rate                      | up to 600 000 waveforms per second                                              |  |

|                                         | action on error                | acquisition stop, beep, print and save                                          |  |

|                                         |                                | waveform                                                                        |  |

|                                         | save/load to file              | test and mask settings (.xml format)                                            |  |

| Mask definition with segments           | number of independent segments | up to 8                                                                         |  |

|                                         | segment definition             | array of points and connecting rule (upper, lower, inner) define segment region |  |

|                                         | segment input                  | point and click on touchscreen, editable list                                   |  |

| Mask definition with tolerance tube     | input signal                   | acquired waveform                                                               |  |

|                                         | definition of tolerance tube   | horizontal width, vertical width, vertical                                      |  |

|                                         |                                | stretch, vertical position                                                      |  |

| Mask definition with eye mask assistant | primary mask shape             |                                                                                 |  |

| (requires R&S®RTO-K12 option)           | type                           | diamond, square, hexagon, octagon                                               |  |

|                                         | dimensions                     | main and secondary height, main and                                             |  |

|                                         |                                | secondary width, depending on selected                                          |  |

|                                         |                                | shape                                                                           |  |

|                                         | position                       | vertical offset, horizontal offset                                              |  |

|                                         | secondary mask shapes          |                                                                                 |  |

|                                         | locations                      | any combination of left, right, top, bottom                                     |  |

|                                         | position                       | horizontal and vertical offset with respect                                     |  |

|                                         |                                | to center of primary mask shape                                                 |  |

| Result statistics                       | category                       | completed acquisitions, remaining                                               |  |

|                                         |                                | acquisitions, state, sample hits, mask hits,                                    |  |

|                                         |                                | fail rate, test result (pass or fail)                                           |  |

| Visualization options                   | waveform style                 | vectors, dots                                                                   |  |

|                                         | violation highlighting         | hits (on/off), highlight persistence                                            |  |

|                                         |                                | (50 ms to 50 s or infinite), waveform color                                     |  |

|                                         |                                | (default: red)                                                                  |  |

|                                         | mask colors                    | configurable colors for mask without                                            |  |

|                                         |                                | violation (default: translucent gray), mask                                     |  |

|                                         |                                | with violation (default: translucent red),                                      |  |

|                                         |                                | mask with contact (default: translucent                                         |  |

|                                         |                                | pale red)                                                                       |  |

## **Waveform math**

| General features      | number of math waveforms            | up to 4                                                                                                                                                                                                                                                            |  |  |

|-----------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                       | number of reference waveforms       | up to 4                                                                                                                                                                                                                                                            |  |  |

|                       | waveform arithmetic                 | user-selectable average or envelope of consecutive waveforms                                                                                                                                                                                                       |  |  |

| Algebraic expressions | user may define complex mathematica | user may define complex mathematical expressions involving waveforms and                                                                                                                                                                                           |  |  |

|                       | math functions                      | add, subtract, multiply, divide, absolute value, square, square root, integrate, differentiate, exp, log <sub>10</sub> , log <sub>e</sub> , log <sub>2</sub> , rescale, sin, cos, tan, arcsin, arccos, arctan, sinh, cosh, tanh, autocorrelation, crosscorrelation |  |  |

|                       | logical operators                   | not, and, nand, or, nor, xor, nxor                                                                                                                                                                                                                                 |  |  |

|                       | relational operators                | Boolean result of =, $\neq$ , >, <, $\leq$ , $\geq$                                                                                                                                                                                                                |  |  |

|                       | frequency domain                    | spectral magnitude and phase, real and imaginary spectra, group delay                                                                                                                                                                                              |  |  |

|                       | digital filter                      | lowpass, highpass                                                                                                                                                                                                                                                  |  |  |

|                       | special functions                   | CDR transform; requires R&S®RTO-K12 option                                                                                                                                                                                                                         |  |  |

| Optimized math        | operators                           | add, subtract, multiply, invert, absolute value, differentiate, log <sub>10</sub> , log <sub>e</sub> , log <sub>2</sub> , rescale, FIR, FFT magnitude                                                                                                              |  |  |

| Spectrum analysis     | FFT magnitude spectrum              |                                                                                                                                                                                                                                                                    |  |  |